2011 IEEE 14th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS 2011) : Cottbus

![PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/85a25301661db8d690501e3d9c7f0e65e07f98f3/5-Table1-1.png)

PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar

![PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/85a25301661db8d690501e3d9c7f0e65e07f98f3/3-Figure1-1.png)

PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar

![PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar](https://ai2-s2-public.s3.amazonaws.com/figures/2017-08-08/85a25301661db8d690501e3d9c7f0e65e07f98f3/4-Figure2-1.png)

PDF] APPLICATION OF I DDT TEST IN SRAM ARRAYS TOWARDS EFFICIENT DETECTION OF WEAK OPENS | Semantic Scholar

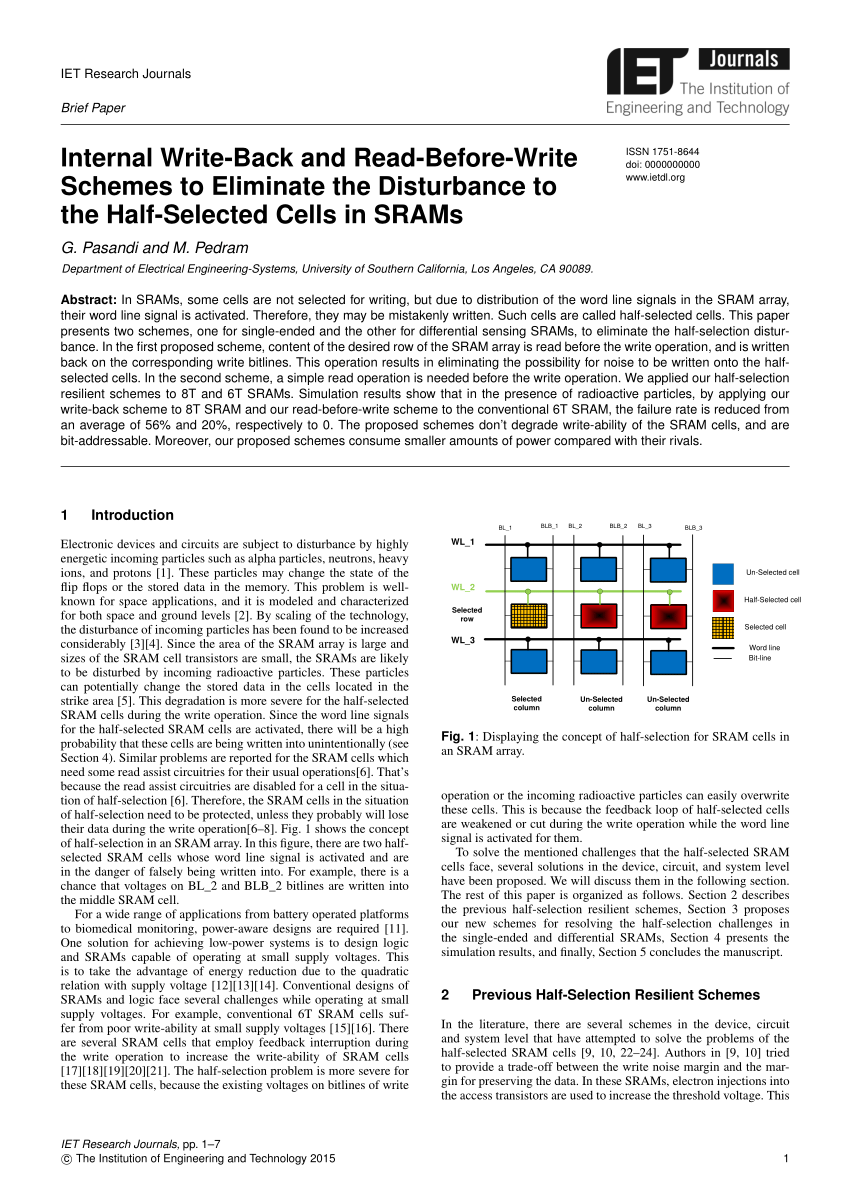

Fault detection as a function of the cycle time, defect size and number... | Download Scientific Diagram

PDF) Internal Write-Back and Read-Before-Write Schemes to Eliminate the Disturbance to the Half-Selected Cells in SRAMs